# dsPIC30F6010 Data Sheet

High-Performance Digital Signal Controllers

© 2004 Microchip Technology Inc. Preliminary Www.DatySheat4U.com

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE. MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, PICMASTER, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2004, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper. 11/12/04

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona and Mountain View, California in October 2003. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# dsPIC30F6010 Enhanced Flash 16-bit Digital Signal Controller

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the *dsPIC30F Family Reference Manual* (DS70046). For more information on the device instruction set and programming, refer to the *dsPIC30F Programmer's Reference Manual* (DS70030).

#### **High-Performance Modified RISC CPU:**

- · Modified Harvard architecture

- C compiler optimized instruction set architecture with flexible Addressing modes

- · 84 base instructions

- · 24-bit wide instructions, 16-bit wide data path

- 144 Kbytes on-chip Flash program space (Instruction words)

- · 8 Kbytes of on-chip data RAM

- · 4 Kbytes of non-volatile data EEPROM

- · Up to 30 MIPs operation:

- DC to 40 MHz external clock input

- 4 MHz-10 MHz oscillator input with PLL active (4x, 8x, 16x)

- · 44 interrupt sources

- 5 external interrupt sources

- 8 user selectable priority levels for each interrupt source

- 4 processor trap sources

- 16 x 16-bit working register array

#### **DSP Engine Features:**

- · Dual data fetch

- · Accumulator write back for DSP operations

- · Modulo and Bit-Reversed Addressing modes

- Two, 40-bit wide accumulators with optional saturation logic

- 17-bit x 17-bit single cycle hardware fractional/ integer multiplier

- All DSP instructions single cycle

- · ± 16-bit single cycle shift

#### **Peripheral Features:**

- · High current sink/source I/O pins: 25 mA/25 mA

- · Timer module with programmable prescaler:

- Five 16-bit timers/counters; optionally pair 16-bit timers into 32-bit timer modules

- 16-bit Capture input functions

- 16-bit Compare/PWM output functions

- 3-wire SPI<sup>™</sup> modules (supports 4 Frame modes)

- I<sup>2</sup>C<sup>™</sup> module supports Multi-Master/Slave mode and 7-bit/10-bit addressing

- · 2 UART modules with FIFO Buffers

- · 2 CAN modules, 2.0B compliant

#### **Motor Control PWM Module Features:**

- · 8 PWM output channels

- Complementary or Independent Output modes

- Edge and Center Aligned modes

- 4 duty cycle generators

- · Dedicated time base

- · Programmable output polarity

- · Dead Time control for Complementary mode

- Manual output control

- · Trigger for A/D conversions

## Quadrature Encoder Interface Module Features:

- · Phase A, Phase B and Index Pulse input

- 16-bit up/down position counter

- · Count direction status

- Position Measurement (x2 and x4) mode

- · Programmable digital noise filters on inputs

- Alternate 16-bit Timer/Counter mode

- · Interrupt on position counter rollover/underflow

#### **Analog Features:**

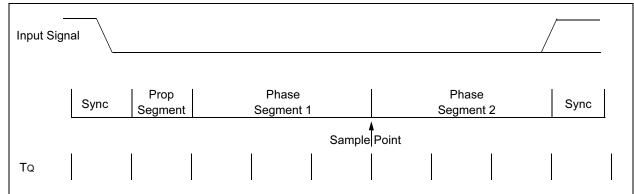

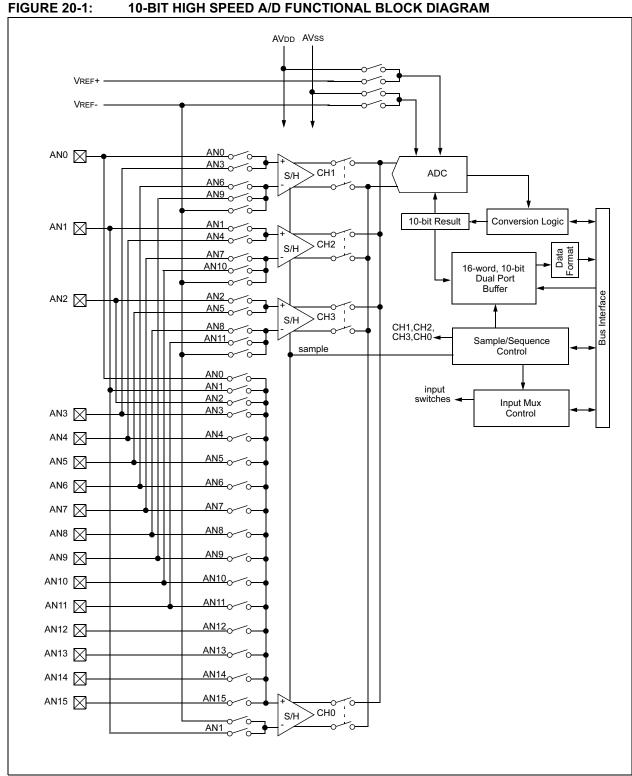

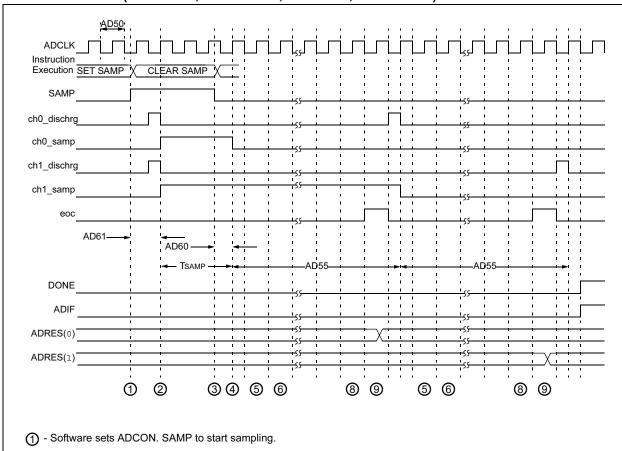

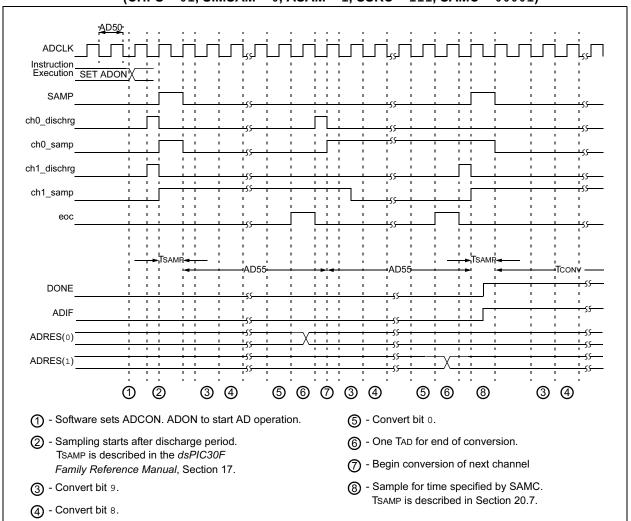

- 10-bit Analog-to-Digital Converter (A/D) with 4 S/H Inputs:

- 500 Ksps conversion rate

- 16 input channels

- Conversion available during Sleep and Idle

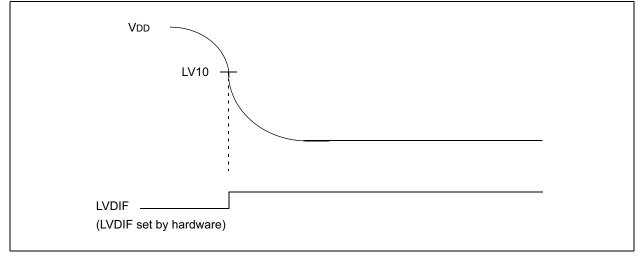

- Programmable Low Voltage Detection (PLVD)

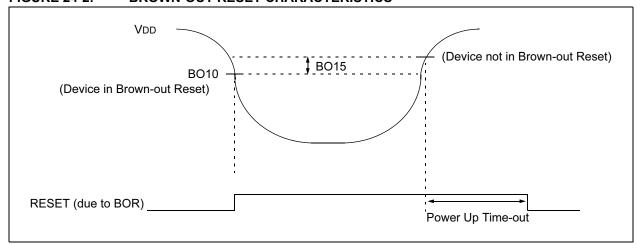

- Programmable Brown-out Detection and Reset generation

#### **Special Microcontroller Features:**

- · Enhanced Flash program memory:

- 10,000 erase/write cycle (min.) for industrial temperature range, 100K (typical)

- · Data EEPROM memory:

- 100,000 erase/write cycle (min.) for industrial temperature range, 1M (typical)

- · Self-reprogrammable under software control

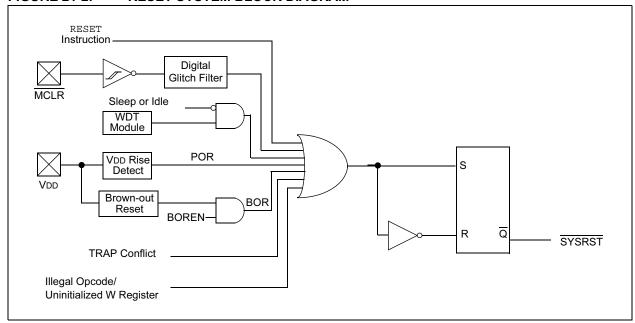

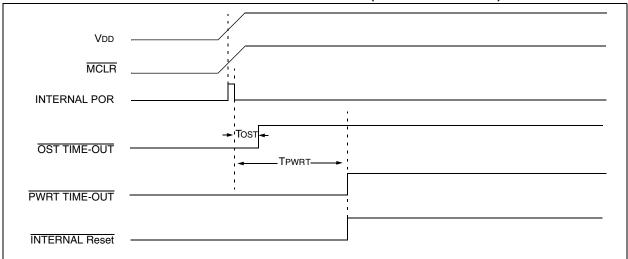

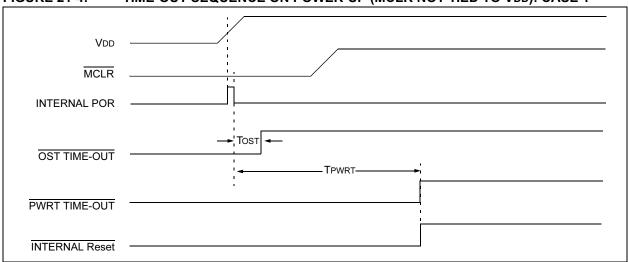

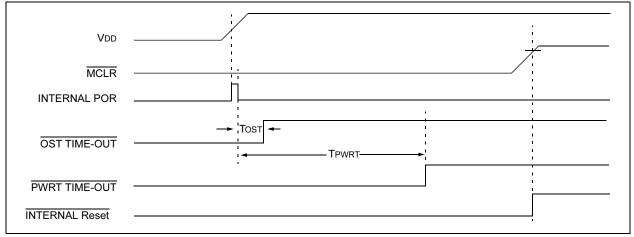

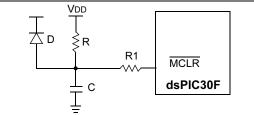

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT) with on-chip low power RC oscillator for reliable operation

- Fail-Safe clock monitor operation detects clock failure and switches to on-chip low power RC oscillator

- · Programmable code protection

- In-Circuit Serial Programming™ (ICSP™)

- · Selectable Power Management modes

- Sleep, Idle and Alternate Clock modes

#### **CMOS Technology:**

- · Low power, high speed Flash technology

- Wide operating voltage range (2.5V to 5.5V)

- · Industrial and Extended temperature ranges

- · Low power consumption

#### dsPIC30F Motor Control and Power Conversion Family\*

| Device       | Pins  | Program<br>Mem. Bytes/<br>Instructions | SRAM<br>Bytes | EEPROM<br>Bytes | Timer<br>16-bit | Input<br>Cap | Output<br>Comp/Std<br>PWM | Moto<br>Control<br>PWM | A/D 10-bit<br>500 Ksps | Quad<br>Enc | UART | SРІ™ | І <sup>2</sup> Стм | CAN |

|--------------|-------|----------------------------------------|---------------|-----------------|-----------------|--------------|---------------------------|------------------------|------------------------|-------------|------|------|--------------------|-----|

| dsPIC30F2010 | 28    | 12K/4K                                 | 512           | 1024            | 3               | 4            | 2                         | 6 ch                   | 6 ch                   | Yes         | 1    | 1    | 1                  | -   |

| dsPIC30F3010 | 28    | 24K/8K                                 | 1024          | 1024            | 5               | 4            | 2                         | 6 ch                   | 6 ch                   | Yes         | 1    | 1    | 1                  | -   |

| dsPIC30F4012 | 28    | 48K/16K                                | 2048          | 1024            | 5               | 4            | 2                         | 6 ch                   | 6 ch                   | Yes         | 1    | 1    | 1                  | 1   |

| dsPIC30F3011 | 40/44 | 24K/8K                                 | 1024          | 1024            | 5               | 4            | 4                         | 6 ch                   | 9 ch                   | Yes         | 2    | 1    | 1                  | -   |

| dsPIC30F4011 | 40/44 | 48K/16K                                | 2048          | 1024            | 5               | 4            | 4                         | 6 ch                   | 9 ch                   | Yes         | 2    | 1    | 1                  | 1   |

| dsPIC30F5015 | 64    | 66K/22K                                | 2048          | 1024            | 5               | 4            | 4                         | 8 ch                   | 16 ch                  | Yes         | 1    | 2    | 1                  | 1   |

| dsPIC30F6010 | 80    | 144K/48K                               | 8192          | 4096            | 5               | 8            | 8                         | 8 ch                   | 16 ch                  | Yes         | 2    | 2    | 1                  | 2   |

<sup>\*</sup> This table provides a summary of the dsPIC30F6010 peripheral features. Other available devices in the dsPIC30F Motor Control and Power Conversion Family are shown for feature comparison.

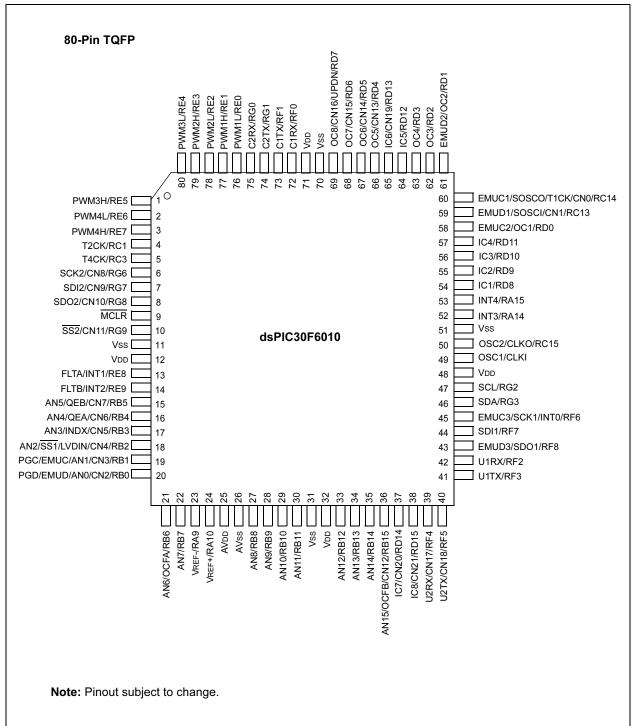

#### Pin Diagram

#### **Table of Contents**

| 1.0   | Device Overview                                            | 5   |

|-------|------------------------------------------------------------|-----|

| 2.0   | CPU Architecture Overview                                  |     |

| 3.0   | Memory Organization                                        | 19  |

| 4.0   | Address Generator Units                                    | 31  |

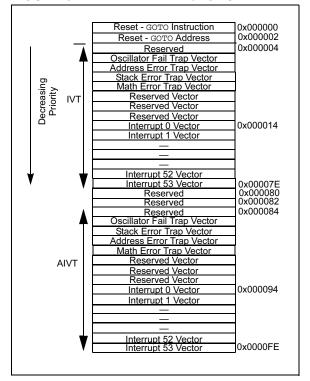

| 5.0   | Interrupts                                                 | 37  |

| 6.0   | Flash Program Memory                                       | 43  |

| 7.0   | Data EEPROM Memory                                         | 49  |

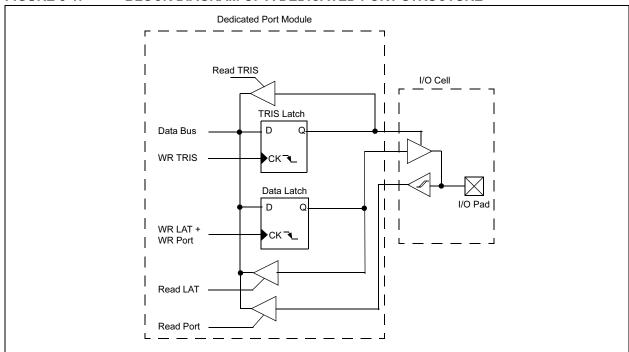

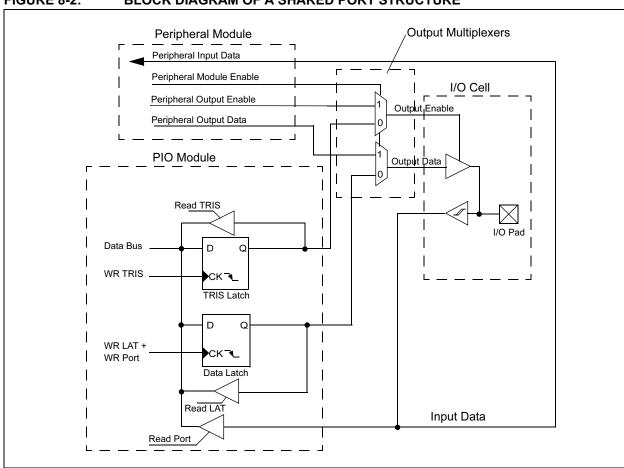

| 8.0   | I/O Ports                                                  | 53  |

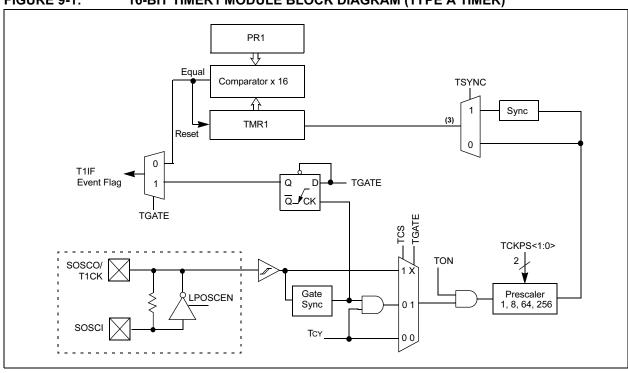

| 9.0   | Timer1 Module                                              | 57  |

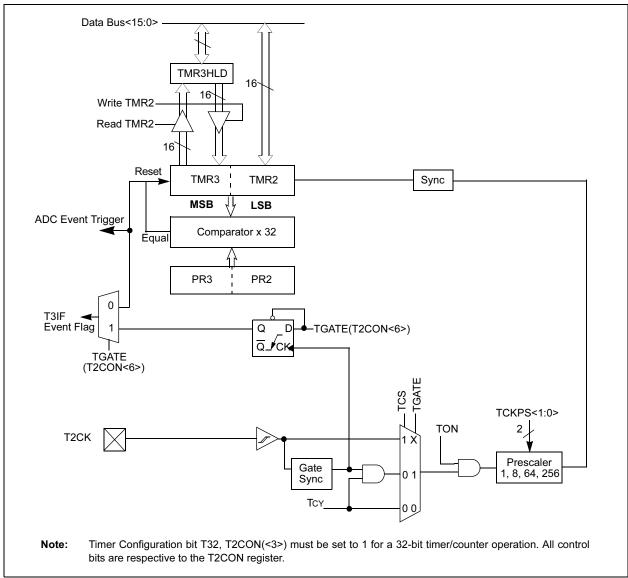

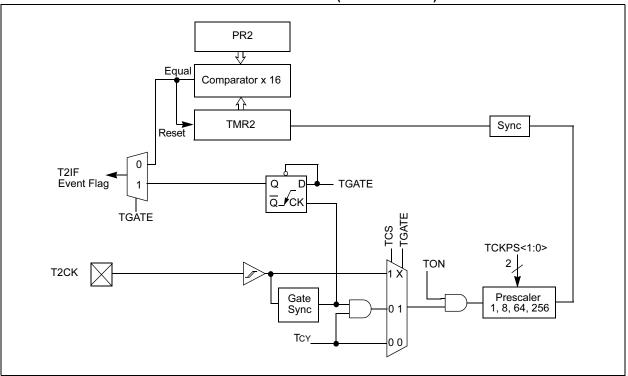

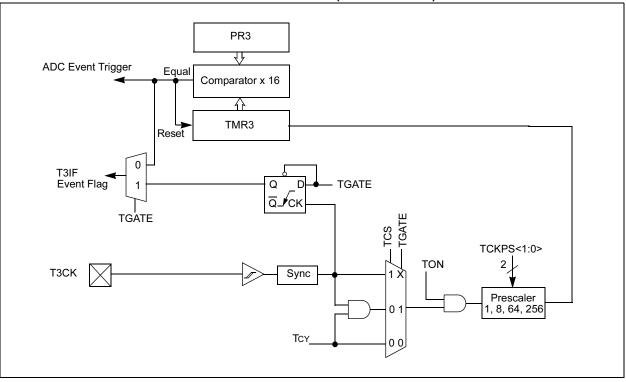

| 10.0  | Timer2/3 Module                                            | 61  |

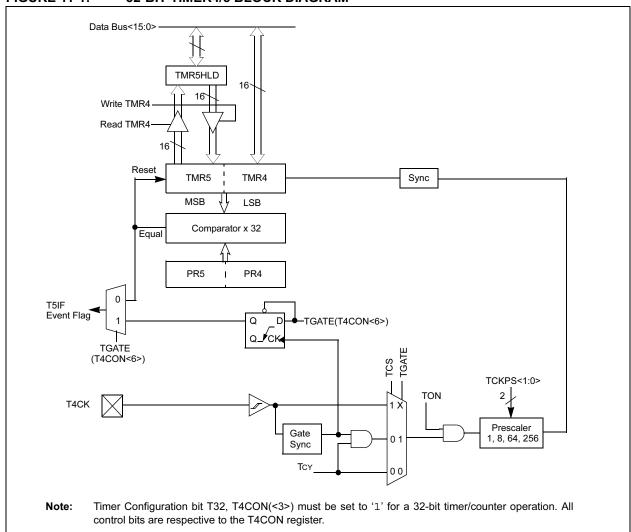

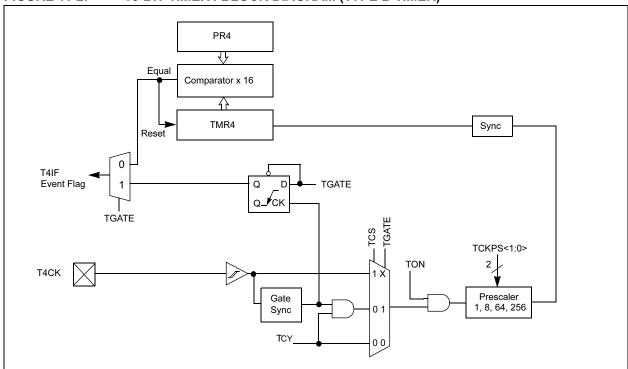

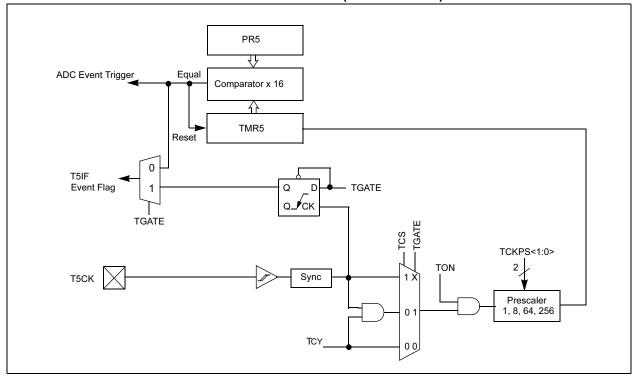

| 11.0  | Timer4/5 Module                                            | 67  |

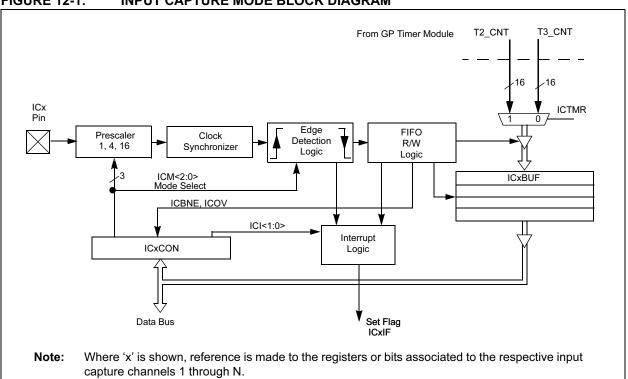

| 12.0  | Input Capture Module                                       | 71  |

| 13.0  | Output Compare Module                                      | 75  |

| 14.0  | Quadrature Encoder Interface (QEI) Module                  | 79  |

| 15.0  | Motor Control PWM Module                                   | 85  |

| 16.0  | SPI™ Module                                                | 95  |

|       | I2C Module                                                 |     |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART) Module  | 107 |

| 19.0  | CAN Module                                                 | 115 |

| 20.0  | 10-bit High Speed Analog-to-Digital Converter (A/D) Module | 127 |

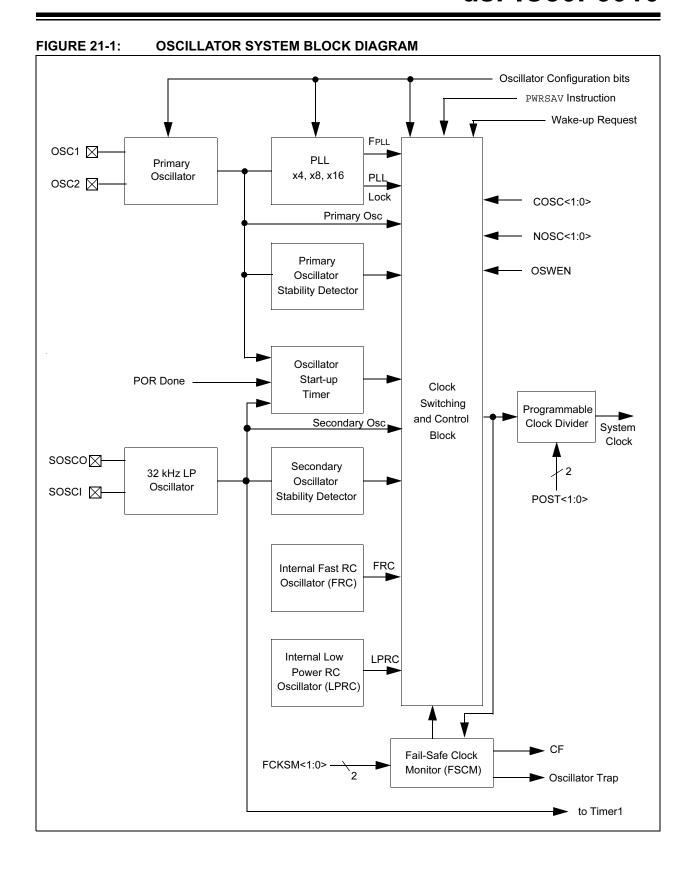

| 21.0  | System Integration                                         | 135 |

|       | Instruction Set Summary                                    |     |

|       | Development Support                                        |     |

|       | Electrical Characteristics                                 |     |

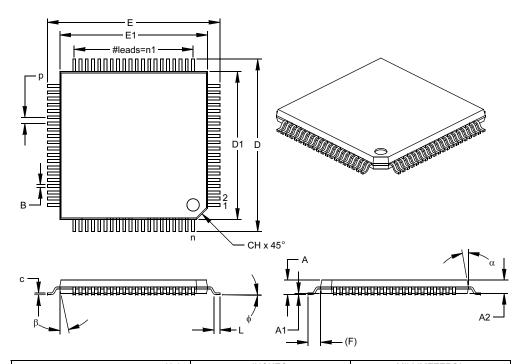

| 25.0  | Packaging Information                                      | 205 |

| On-L  | ine Support                                                | 213 |

| •     | ems Information and Upgrade Hot Line                       |     |

| Read  | der Response                                               | 214 |

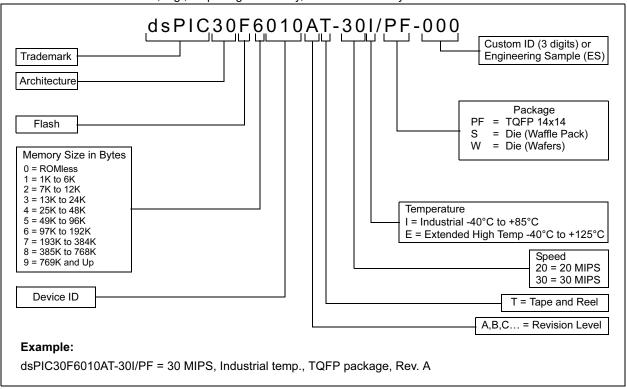

| Produ | uct Identification System                                  | 215 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### Customer Notification System

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

#### 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the *dsPIC30F Family Reference Manual* (DS70046). For more information on the device instruction set and programming, refer to the *dsPIC30F Programmer's Reference Manual* (DS70030).

This document contains device specific information for the dsPIC30F6010 device. The dsPIC30F devices contain extensive Digital Signal Processor (DSP) functionality within a high-performance 16-bit microcontroller (MCU) architecture. Figure 1-1 shows a device block diagram for the dsPIC30F6010 device.

Y Data Bus X Data Bus 16 16 /16 16 VREF-/RA9 16 VREF+/RA10 Data Latch Data Latch Interrupt INT3/RA14 PSV & Table X Data RAM Controller Y Data Data Access Control Block INT4/RA15 RAM 116 (4 Kbytes) (4 Kbytes) PORTA Address Address 24 Latch Latch PGC/EMUC/AN0/CN2/RB0 PGD/EMUD/AN1/CN3/RB1 **√**16 √16 16 AN2/SS1/LVDIN/CN4/RB2 24 X RAGU Y AGU AN3/INDX/CN5/RB3 PCŮ PCH PCL X WAGU AN4/QEA/CN6/RB4 Program Counter AN5/QEB/CN7/RB5 Stack Control Loop Control Address Latch AN6/OCFA/RB6 Logic Logic AN7/RB7 Program Memory (144 Kbytes) AN8/RB8 AN9/RB9 Data EEPROM AN10/RB10 (4 Kbytes) Effective Address AN11/RB11 16 Data Latch AN12/RB12 AN13/RB13 AN14/RB14 ROM Latch 116 AN15/OCFB/CN12/RB15 24 PORTB T2CK/RC1 IR T4CK/RC3 16 EMUD1/SOSCI/CN1/RC13 16 EMUC1/SOSCO/T1CK/CN0/RC14 16 x 16 OSC2/CLKO/RC15 W Reg Array Decode Instruction ₩6₩6 Decode & Control EMUC2/OC1/RD0 EMUD2/OC2/RD1 Control Signals V V V V to Various Blocks OC3/RD2 DSP OC4/RD3 Divide Power-up Engine OC5/CN13/RD4 Unit Timer OC6/CN14/RD5 OC7/CN15/RD6 Oscillator Timing Generation OSC1/CLKI OC8/CN16/UPDN/RD7 Start-up Time IC1/RD8 ALU<16> POR/BOR IC2/RD9 Reset IC3/RD10  $\boxtimes$ 16 IC4/RD11 16 Watchdog MCLR IC5/RD12 IC6/CN19/RD13  $\times$ Low Voltage IC7/CN20/RD14 Detect VDD, VSS IC8/CN21/RD15 AVDD, AVSS PORTD PWM1L/RE0 Input Output CAN1, PWM1H/RE1 I<sup>2</sup>C 10-bit ADC Capture Compare CAN2 PWM2L/RE2 Module Module PWM2H/RE3 PWM3I /RF4 PWM3H/RE5 ļĹ ][ PWM4L/RE6 PWM4H/RE7 UART1, FI TA/INT1/RF8 SPI1 Motor Control QEI Timers UART2 SPI2 FLTB/INT2/RE9 PWM PORTE C1RX/RF0 C2RX/RG0 C1TX/RF1 C2TX/RG1 U1RX/RF2 SCL/RG2 U1TX/RF3 SDA/RG3 U2RX/CN17/RF4 SCK2/CN8/RG6 U2TX/CN18/RF5 SDI2/CN9/RG7 EMUC3/SCK1/INT0/RF6 SDO2/CN10/RG8 SDI1/RF7 SS2/CN11/RG9 EMUD3/SDO1/RF8 **PORTG**

FIGURE 1-1: dsPIC30F6010 BLOCK DIAGRAM

Table 1-1 provides a brief description of the device I/O pinout and the functions that are multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

TABLE 1-1: dsPIC30F6010 I/O PIN DESCRIPTIONS

| Pin Name                                                           | Pin<br>Type                                   | Buffer<br>Type                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                                                           | I                                             | Analog                                       | Analog input channels. AN0 and AN1 are also used for device programming data and clock inputs, respectively.                                                                                                                                                                                                                                                                                                                                                                            |

| AVDD                                                               | Р                                             | Р                                            | Positive supply for analog module.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AVss                                                               | Р                                             | Р                                            | Ground reference for analog module.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLKI<br>CLKO                                                       | 0                                             | ST/CMOS                                      | External clock source input. Always associated with OSC1 pin function. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function.                                                                                                                                                                                                                               |

| CN0-CN23                                                           | I                                             | ST                                           | Input change notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                                                                                                                                                  |

| COFS<br>CSCK<br>CSDI<br>CSDO                                       | I/O<br>I/O<br>I O                             | ST<br>ST<br>ST                               | Data Converter Interface frame synchronization pin.  Data Converter Interface serial clock input/output pin.  Data Converter Interface serial data input pin.  Data Converter Interface serial data output pin.                                                                                                                                                                                                                                                                         |

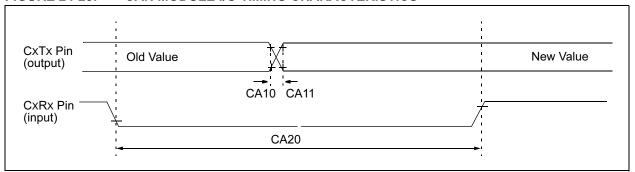

| C1RX<br>C1TX<br>C2RX<br>C2TX                                       | -<br>0<br>-<br>0                              | ST<br>—<br>ST<br>—                           | CAN1 bus receive pin. CAN1 bus transmit pin. CAN2 bus receive pin. CAN2 bus transmit pin.                                                                                                                                                                                                                                                                                                                                                                                               |

| EMUD<br>EMUC<br>EMUD1<br>EMUC1<br>EMUD2<br>EMUC2<br>EMUD3<br>EMUC3 | 1/O<br>1/O<br>1/O<br>1/O<br>1/O<br>1/O<br>1/O | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST | ICD Primary Communication Channel data input/output pin. ICD Primary Communication Channel clock input/output pin. ICD Secondary Communication Channel data input/output pin. ICD Secondary Communication Channel clock input/output pin. ICD Tertiary Communication Channel data input/output pin. ICD Tertiary Communication Channel clock input/output pin. ICD Quaternary Communication Channel data input/output pin. ICD Quaternary Communication Channel clock input/output pin. |

| IC1-IC8                                                            | I                                             | ST                                           | Capture inputs 1 through 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| INDX<br>QEA                                                        | l<br>I                                        | ST<br>ST                                     | Quadrature Encoder Index Pulse input. Quadrature Encoder Phase A input in QEI mode. Auxiliary Timer External Clock/Gate input in Timer mode.                                                                                                                                                                                                                                                                                                                                            |

| QEB                                                                | I                                             | ST                                           | Quadrature Encoder Phase A input in QEI mode.<br>Auxiliary Timer External Clock/Gate input in Timer mode.                                                                                                                                                                                                                                                                                                                                                                               |

| UPDN                                                               | 0                                             | CMOS                                         | Position Up/Down Counter Direction State.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INT0<br>INT1<br>INT2<br>INT3<br>INT4                               |                                               | ST<br>ST<br>ST<br>ST<br>ST                   | External interrupt 0. External interrupt 1. External interrupt 2. External interrupt 3. External interrupt 4.                                                                                                                                                                                                                                                                                                                                                                           |

| LVDIN                                                              | I                                             | Analog                                       | Low Voltage Detect Reference Voltage input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Legend: CMOS = CMOS compatible input or output Analog = Analog input

ST = Schmitt Trigger input with CMOS levels O = Output

I = Input P = Power

dsPIC30F6010 I/O PIN DESCRIPTIONS (CONTINUED) **TABLE 1-1:**

| IABLE 1-1:   |             |                | O PIN DESCRIPTIONS (CONTINUED)                                                                                                                                                                                           |

|--------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name     | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                              |

| FLTA         | I           | ST             | PWM Fault A input.                                                                                                                                                                                                       |

| FLTB         | I           | ST             | PWM Fault B input.                                                                                                                                                                                                       |

| PWM1L        | 0           |                | PWM 1 Low output.                                                                                                                                                                                                        |

| PWM1H        | 0           |                | PWM 1 High output.                                                                                                                                                                                                       |

| PWM2L        | 0           |                | PWM 2 Low output.                                                                                                                                                                                                        |

| PWM2H        | 0           |                | PWM 2 High output.                                                                                                                                                                                                       |

| PWM3L        | 0           | _              | PWM 3 Low output.                                                                                                                                                                                                        |

| PWM3H        | 0           | _              | PWM 3 High output.                                                                                                                                                                                                       |

| PWM4L        | 0           | _              | PWM 4 Low output.                                                                                                                                                                                                        |

| PWM4H        | 0           |                | PWM 4 High output.                                                                                                                                                                                                       |

| MCLR         | I/P         | ST             | Master Clear (Reset) input or programming voltage input. This pin is an active low Reset to the device.                                                                                                                  |

| OCFA         | I           | ST             | Compare Fault A input (for Compare channels 1, 2, 3 and 4).                                                                                                                                                              |

| OCFB         | ı           | ST             | Compare Fault B input (for Compare channels 5, 6, 7 and 8).                                                                                                                                                              |

| OC1-OC8      | 0           | _              | Compare outputs 1 through 8.                                                                                                                                                                                             |

| OSC1<br>OSC2 | I<br>I/O    | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. |

| DOD          | 1/0         | 0.7            |                                                                                                                                                                                                                          |

| PGD          | I/O         | ST             | In-Circuit Serial Programming data input/output pin.                                                                                                                                                                     |

| PGC          | I           | ST             | In-Circuit Serial Programming clock input pin.                                                                                                                                                                           |

| RA9-RA10     | I/O         | ST             | PORTA is a bi-directional I/O port.                                                                                                                                                                                      |

| RA14-RA15    | I/O         | ST             |                                                                                                                                                                                                                          |

| RB0-RB15     | I/O         | ST             | PORTB is a bi-directional I/O port.                                                                                                                                                                                      |

| RC1          | I/O         | ST             | PORTC is a bi-directional I/O port.                                                                                                                                                                                      |

| RC3          | I/O         | ST             | ,                                                                                                                                                                                                                        |

| RC13-RC15    | I/O         | ST             |                                                                                                                                                                                                                          |

| RD0-RD15     | I/O         | ST             | PORTD is a bi-directional I/O port.                                                                                                                                                                                      |

| RE0-RE9      | I/O         | ST             | PORTE is a bi-directional I/O port.                                                                                                                                                                                      |

| RF0-RF8      | I/O         | ST             | PORTF is a bi-directional I/O port.                                                                                                                                                                                      |

| RG0-RG3      | I/O         | ST             | PORTG is a bi-directional I/O port.                                                                                                                                                                                      |

| RG6-RG9      | 1/0         | ST             | TONTO IS A DI-UITECUIOTIAI I/O POIT.                                                                                                                                                                                     |

| SCK1         | I/O         | ST             | Synchronous serial clock input/output for SPI™ #1.                                                                                                                                                                       |

| SDI1         | ı, C        | ST             | SPI #1 Data In.                                                                                                                                                                                                          |

| SDO1         | Ö           | _              | SPI #1 Data Out.                                                                                                                                                                                                         |

| SS1          | Ī           | ST             | SPI #1 Slave Synchronization.                                                                                                                                                                                            |

| SCK2         | I/O         | ST             | Synchronous serial clock input/output for SPI #2.                                                                                                                                                                        |

| SDI2         | ı, o        | ST             | SPI #2 Data In.                                                                                                                                                                                                          |

| SDO2         | 0           | _              | SPI #2 Data Out.                                                                                                                                                                                                         |

| SS2          | I           | ST             | SPI #2 Slave Synchronization.                                                                                                                                                                                            |

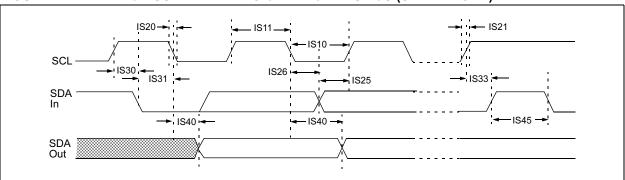

| SCL          | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C.                                                                                                                                                              |

| SDA          | I/O         | ST             | Synchronous serial data input/output for I <sup>2</sup> C.                                                                                                                                                               |

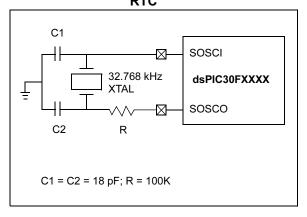

| sosco        | 0           |                | 32 kHz low power oscillator crystal output.                                                                                                                                                                              |

| SOSCI        | Ĭ           | ST/CMOS        | 32 kHz low power oscillator crystal input. ST buffer when configured in RC                                                                                                                                               |

|              | '           | 31,01000       | mode; CMOS otherwise.                                                                                                                                                                                                    |

|              |             | L              | mode, omeo onerwise.                                                                                                                                                                                                     |

Legend: CMOS = CMOS compatible input or output

Analog = Analog input ST = Schmitt Trigger input with CMOS levels 0 = Output Power

= Input

TABLE 1-1: dsPIC30F6010 I/O PIN DESCRIPTIONS (CONTINUED)

| Pin Name | Pin<br>Type | Buffer<br>Type | Description                              |

|----------|-------------|----------------|------------------------------------------|

| T1CK     | I           | ST             | Timer1 external clock input.             |

| T2CK     | I           | ST             | Timer2 external clock input.             |

| T3CK     | I           | ST             | Timer3 external clock input.             |

| T4CK     | I           | ST             | Timer4 external clock input.             |

| T5CK     | I           | ST             | Timer5 external clock input.             |

| U1RX     | I           | ST             | UART1 Receive.                           |

| U1TX     | 0           |                | UART1 Transmit.                          |

| U1ARX    | I           | ST             | UART1 Alternate Receive.                 |

| U1ATX    | 0           |                | UART1 Alternate Transmit.                |

| U2RX     | I           | ST             | UART2 Receive.                           |

| U2TX     | 0           | _              | UART2 Transmit.                          |

| VDD      | Р           | _              | Positive supply for logic and I/O pins.  |

| Vss      | Р           |                | Ground reference for logic and I/O pins. |

| VREF+    | Ī           | Analog         | Analog Voltage Reference (High) input.   |

| VREF-    | I           | Analog         | Analog Voltage Reference (Low) input.    |

Legend: CMOS = CMOS compatible input or output Analog = Analog input ST = Schmitt Trigger input with CMOS levels O = Output P = Power

© 2004 Microchip Technology Inc. Preliminary DS70119D-page 9

NOTES:

# 2.0 CPU ARCHITECTURE OVERVIEW

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the *dsPIC30F Family Reference Manual* (DS70046). For more information on the device instruction set and programming, refer to the *dsPIC30F Programmer's Reference Manual* (DS70030).

This document provides a summary of the dsPIC30F6010 CPU and peripheral function. For a complete description of this functionality, please refer to the dsPIC30F Family Reference Manual (DS70046).

#### 2.1 Core Overview

The core has a 24-bit instruction word. The Program Counter (PC) is 23 bits wide with the Least Significant (LS) bit always clear (see Section 3.1), and the Most Significant (MS) bit is ignored during normal program execution, except for certain specialized instructions. Thus, the PC can address up to 4M instruction words of user program space. An instruction pre-fetch mechanism is used to help maintain throughput. Program loop constructs, free from loop count management overhead, are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The working register array consists of 16x16-bit registers, each of which can act as data, address or offset registers. One working register (W15) operates as a software stack pointer for interrupts and calls.

The data space is 64 Kbytes (32K words) and is split into two blocks, referred to as X and Y data memory. Each block has its own independent Address Generation Unit (AGU). Most instructions operate solely through the X memory AGU, which provides the appearance of a single unified data space. The Multiply-Accumulate (MAC) class of dual source DSP instructions operate through both the X and Y AGUs, splitting the data address space into two parts (see Section 3.2). The X and Y data space boundary is device specific and cannot be altered by the user. Each data word consists of 2 bytes, and most instructions can address data either as words or bytes.

There are two methods of accessing data stored in program memory:

The upper 32 Kbytes of data space memory can be mapped into the lower half (user space) of program space at any 16K program word boundary, defined by the 8-bit Program Space Visibility Page (PSVPAG) register. This lets any instruction access program space as if it were data space, with a limitation that the access requires an additional cycle. Moreover, only the lower 16 bits of each instruction word can be accessed using this method.  Linear indirect access of 32K word pages within program space is also possible using any working register, via table read and write instructions.

Table read and write instructions can be used to access all 24 bits of an instruction word.

Overhead-free circular buffers (modulo addressing) are supported in both X and Y address spaces. This is primarily intended to remove the loop overhead for DSP algorithms.

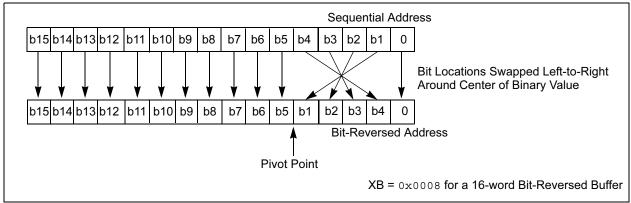

The X AGU also supports bit-reversed addressing on destination effective addresses, to greatly simplify input or output data reordering for radix-2 FFT algorithms. Refer to Section 4.0 for details on modulo and bit-reversed addressing.

The core supports Inherent (no operand), Relative, Literal, Memory Direct, Register Direct, Register Indirect, Register Offset and Literal Offset Addressing modes. Instructions are associated with predefined Addressing modes, depending upon their functional requirements.

For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, 3-operand instructions are supported, allowing C = A+B operations to be executed in a single cycle.

A DSP engine has been included to significantly enhance the core arithmetic capability and throughput. It features a high speed 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bi-directional barrel shifter. Data in the accumulator or any working register can be shifted up to 16 bits right or 16 bits left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC class of instructions can concurrently fetch two data operands from memory, while multiplying two W registers. To enable this concurrent fetching of data operands, the data space has been split for these instructions and linear for all others. This has been achieved in a transparent and flexible manner, by dedicating certain working registers to each address space for the MAC class of instructions.

The core does not support a multi-stage instruction pipeline. However, a single stage instruction pre-fetch mechanism is used, which accesses and partially decodes instructions a cycle ahead of execution, in order to maximize available execution time. Most instructions execute in a single cycle, with certain exceptions.

The core features a vectored exception processing structure for traps and interrupts, with 62 independent vectors. The exceptions consist of up to 8 traps (of which 4 are reserved) and 54 interrupts. Each interrupt is prioritized based on a user assigned priority between 1 and 7 (1 being the lowest priority and 7 being the highest) in conjunction with a predetermined 'natural order'. Traps have fixed priorities, ranging from 8 to 15.

#### 2.2 Programmer's Model

The programmer's model is shown in Figure 2-1 and consists of 16x16-bit working registers (W0 through W15), 2x40-bit accumulators (AccA and AccB), STATUS register (SR), Data Table Page register (TBLPAG), Program Space Visibility Page register (PSVPAG), DO and REPEAT registers (DOSTART, DOEND, DCOUNT and RCOUNT), and Program Counter (PC). The working registers can act as data, address or offset registers. All registers are memory mapped. W0 acts as the W register for file register addressing.

Some of these registers have a shadow register associated with each of them, as shown in Figure 2-1. The shadow register is used as a temporary holding register and can transfer its contents to or from its host register upon the occurrence of an event. None of the shadow registers are accessible directly. The following rules apply for transfer of registers into and out of shadows.

- PUSH.S and POP.S W0, W1, W2, W3, SR (DC, N, OV, Z and C bits only) are transferred.

- DO instruction DOSTART, DOEND, DCOUNT shadows are pushed on loop start, and popped on loop end.

When a byte operation is performed on a working register, only the Least Significant Byte of the target register is affected. However, a benefit of memory mapped working registers is that both the Least and Most Significant Bytes can be manipulated through byte wide data memory space accesses.

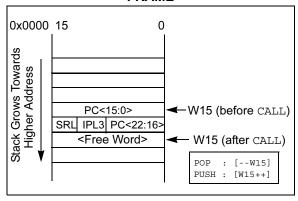

#### 2.2.1 SOFTWARE STACK POINTER/ FRAME POINTER

The dsPIC® devices contain a software stack. W15 is the dedicated software stack pointer (SP), and will be automatically modified by exception processing and subroutine calls and returns. However, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies the reading, writing and manipulation of the stack pointer (e.g., creating stack frames).

**Note:** In order to protect against misaligned stack accesses, W15<0> is always clear.

W15 is initialized to 0x0800 during a Reset. The user may reprogram the SP during initialization to any location within data space.

W14 has been dedicated as a stack frame pointer as defined by the  ${\tt LNK}$  and  ${\tt ULNK}$  instructions. However, W14 can be referenced by any instruction in the same manner as all other W registers.

#### 2.2.2 STATUS REGISTER

The dsPIC core has a 16-bit Status Register (SR), the LS Byte of which is referred to as the SR Low Byte (SRL) and the MS Byte as the SR High Byte (SRH). See Figure 2-1 for SR layout.

SRL contains all the MCU ALU operation status flags (including the Z bit), as well as the CPU Interrupt Priority Level status bits, IPL<2:0>, and the REPEAT active status bit, RA. During exception processing, SRL is concatenated with the MS Byte of the PC to form a complete word value which is then stacked.

The upper byte of the SR register contains the DSP Adder/Subtractor status bits, the DO Loop Active bit (DA) and the Digit Carry (DC) status bit.

#### 2.2.3 PROGRAM COUNTER

The Program Counter is 23 bits wide. Bit 0 is always clear. Therefore, the PC can address up to 4M instruction words.

FIGURE 2-1: dsPIC30F6010 PROGRAMMER'S MODEL D15 D0 W0/WREG PUSH.S Shadow | W1 DO Shadow W2 W3 Legend W4 **DSP** Operand W5 Registers W6 W7 Working Registers W8 W9 **DSP Address** W10 Registers W11 W12/DSP Offset W13/DSP Write Back W14/Frame Pointer W15/Stack Pointer **SPLIM** Stack Pointer Limit Register AD39 AD31 AD15 AD0 DSP AccA Accumulators AccB PC22 PC0 0 **Program Counter** 0 **TBLPAG** Data Table Page Address **PSVPAG** Program Space Visibility Page Address RCOUNT **REPEAT Loop Counter DCOUNT** DO Loop Counter **DOSTART** DO Loop Start Address 22 DO Loop End Address DOEND 15 CORCON Core Configuration Register OA ОВ SA SB OAB SAB DA DC IPL2 IPL1 IPL0 RA Ν OV Ζ С Status Register SRH

#### 2.3 Divide Support

The dsPIC devices feature a 16/16-bit signed fractional divide operation, as well as 32/16-bit and 16/16-bit signed and unsigned integer divide operations, in the form of single instruction iterative divides. The following instructions and data sizes are supported:

- 1. DIVF 16/16 signed fractional divide

- 2. DIV.sd 32/16 signed divide

- 3. DIV.ud 32/16 unsigned divide

- 4. DIV.sw 16/16 signed divide

- 5. DIV.uw 16/16 unsigned divide

The divide instructions must be executed within a REPEAT loop. Any other form of execution (e.g. a series of discrete divide instructions) will not function correctly because the instruction flow depends on RCOUNT. The divide instruction does not automatically set up the RCOUNT value, and it must, therefore, be explicitly and correctly specified in the REPEAT instruction, as shown in Table 2-1 (REPEAT will execute the target instruction {operand value+1} times). The REPEAT loop count must be set up for 18 iterations of the DIV/DIVF instruction. Thus, a complete divide operation requires 19 cycles.

**Note:** The Divide flow is interruptible. However, the user needs to save the context as appropriate.

TABLE 2-1: DIVIDE INSTRUCTIONS

| Instruction       | Function                                                           |

|-------------------|--------------------------------------------------------------------|

| DIVF              | Signed fractional divide: Wm/Wn → W0; Rem → W1                     |

| DIV.sd            | Signed divide: (Wm+1:Wm)/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1 |

| DIV.sw (or DIV.s) | Signed divide: Wm/Wn → W0; Rem → W1                                |

| DIV.ud            | Unsigned divide: (Wm+1:Wm)/Wn → W0; Rem → W1                       |

| DIV.uw (or DIV.u) | Unsigned divide: Wm/Wn → W0; Rem → W1                              |

#### 2.4 DSP Engine

The DSP engine consists of a high speed 17-bit x 17-bit multiplier, a barrel shifter, and a 40-bit adder/ Subtractor (with two target accumulators, round and saturation logic).

The dsPIC30F devices have a single instruction flow which can execute either DSP or MCU instructions. Many of the hardware resources are shared between the DSP and MCU instructions. For example, the instruction set has both DSP and MCU Multiply instructions which use the same hardware multiplier.

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations, which require no additional data. These instructions are  $\mathtt{ADD}$ ,  $\mathtt{SUB}$  and  $\mathtt{NEG}$ .

The DSP engine has various options selected through various bits in the CPU Core Configuration Register (CORCON), as listed below:

- 1. Fractional or integer DSP multiply (IF).

- 2. Signed or unsigned DSP multiply (US).

- 3. Conventional or convergent rounding (RND).

- 4. Automatic saturation on/off for AccA (SATA).

- 5. Automatic saturation on/off for AccB (SATB).

- Automatic saturation on/off for writes to data memory (SATDW).

- 7. Accumulator Saturation mode selection (ACCSAT).

Note: For CORCON layout, see Table 4-2.

A block diagram of the DSP engine is shown in Figure 2-2.

TABLE 2-2: DSP INSTRUCTION SUMMARY

| Instruction | Algebraic Operation |

|-------------|---------------------|

| CLR         | A = 0               |

| ED          | $A = (x - y)^2$     |

| EDAC        | $A = A + (x - y)^2$ |

| MAC         | A = A + (x * y)     |

| MOVSAC      | No change in A      |

| MPY         | A = x * y           |

| MPY.N       | A = - x * y         |

| MSC         | A = A - x * y       |

40 Round t 16 40-bit Accumulator A 40 40-bit Accumulator B Logic Carry/Borrow Out Saturate Adder Carry/Borrow In Negate 40 40 40 Barrel 16 Shifter X Data Bus 40 Sign-Extend Y Data Bus 32 16 Zero Backfill 32 33 17-bit Multiplier/Scaler 16 To/From W Array

FIGURE 2-2: **DSP ENGINE BLOCK DIAGRAM**

#### 2.4.1 MULTIPLIER

The 17x17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17x17-bit multiplier/ scaler is a 33-bit value, which is sign-extended to 40 bits. Integer data is inherently represented as a signed two's complement value, where the MSB is defined as a sign bit. Generally speaking, the range of an N-bit two's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ . For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF), including 0. For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,645 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a two's complement fraction, where the MSB is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit two's complement fraction with this implied radix point is -1.0 to (1-2 $^{1-N}$ ). For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF), including 0 and has a precision of 3.01518x10 $^{-5}$ . In Fractional mode, a 16x16 multiply operation generates a 1.31 product, which has a precision of 4.65661x10 $^{-10}$ .

The same multiplier is used to support the MCU multiply instructions, which include integer 16-bit signed, unsigned and mixed sign multiplies.

The MUL instruction may be directed to use byte or word sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

### 2.4.2 DATA ACCUMULATORS AND ADDER/SUBTRACTOR

The data accumulator consists of a 40-bit adder/subtractor with automatic sign extension logic. It can select one of two accumulators (A or B) as its preaccumulation source and post-accumulation destination. For the  ${\tt ADD}$  and  ${\tt LAC}$  instructions, the data to be accumulated or loaded can be optionally scaled via the barrel shifter, prior to accumulation.

### 2.4.2.1 Adder/Subtractor, Overflow and Saturation

The adder/subtractor is a 40-bit adder with an optional zero input into one side and either true or complement data into the other input. In the case of addition, the carry/borrow input is active high and the other input is true data (not complemented), whereas in the case of subtraction, the carry/borrow input is active low and the other input is complemented. The adder/subtractor generates overflow status bits SA/SB and OA/OB, which are latched and reflected in the status register.

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block which controls accumulator data saturation, if selected. It uses the result of the adder, the overflow status bits described above, and the SATA/B (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six status register bits have been provided to support saturation and overflow; they are:

OA: AccA overflowed into guard bits

2. OB:

AccB overflowed into guard bits

3. SA

AccA saturated (bit 31 overflow and saturation) or

AccA overflowed into guard bits and saturated (bit 39 overflow and saturation)

4 SR

AccB saturated (bit 31 overflow and saturation) or

AccB overflowed into guard bits and saturated (bit 39 overflow and saturation)

5. OAB:

Logical OR of OA and OB

6. SAB:

Logical OR of SA and SB

The OA and OB bits are modified each time data passes through the adder/Subtractor. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when set and the corresponding overflow trap flag enable bit (OVATEN, OVBTEN) in the INTCON1 register (refer to Section 5.0) is set. This allows the user to take immediate action, for example, to correct system gain.

The SA and SB bits are modified each time data passes through the adder/subtractor, but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation, or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow and thus indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The overflow and saturation status bits can optionally be viewed in the Status Register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the Status Register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This would be useful for complex number arithmetic which typically uses both the accumulators.

The device supports three Saturation and Overflow modes.

- 1. Bit 39 Overflow and Saturation:

- When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFFF) or maximally negative 9.31 value (0x8000000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (e.g., gain calculations).

- 2. Bit 31 Overflow and Saturation:

When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFFF) or maximally negative 1.31 value (0x0080000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used (so the OA, OB or OAB bits are never set).

3. Bit 39 Catastrophic Overflow

The bit 39 overflow status bit from the adder is used to set the SA or SB bit, which remain set until cleared by the user. No saturation operation is performed and the accumulator is allowed to overflow (destroying its sign). If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

#### 2.4.2.2 Accumulator 'Write Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- W13, Register Direct:

The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13]+=2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

#### 2.4.2.3 Round Logic

The round logic is a combinational block, which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the LS Word is simply discarded.

Conventional rounding takes bit 15 of the accumulator, zero-extends it and adds it to the ACCxH word (bits 16 through 31 of the accumulator). If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding operations, the value will tend to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. If this is the case, the LS bit (bit 16 of the accumulator) of ACCxH is examined. If it is '1', ACCxH is incremented. If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme will remove any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC) or rounded (SAC.R) version of the contents of the target accumulator to data memory, via the X bus (subject to data saturation, see Section 2.4.2.4). Note that for the MAC class of instructions, the accumulator write back operation will function in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

#### 2.4.2.4 Data Space Write Saturation

In addition to adder/subtractor saturation, writes to data space may also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly. For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF. For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000. The MS bit of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

#### 2.4.3 BARREL SHIFTER

The barrel shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value will shift the operand right. A negative value will shift the operand left. A value of 0 will not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 to 31 for right shifts, and bit positions 0 to 15 for left shifts.

#### 3.0 MEMORY ORGANIZATION

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the *dsPIC30F Family Reference Manual* (DS70046). For more information on the device instruction set and programming, refer to the *dsPIC30F Programmer's Reference Manual* (DS70030).

#### 3.1 Program Address Space

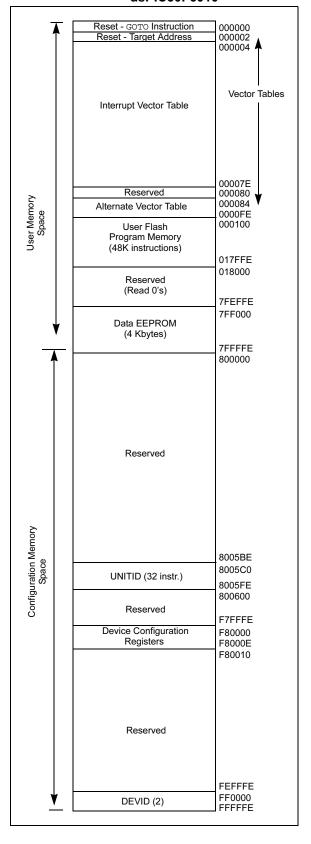

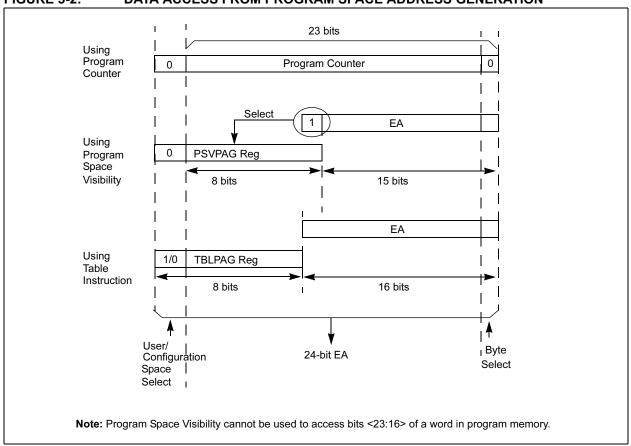

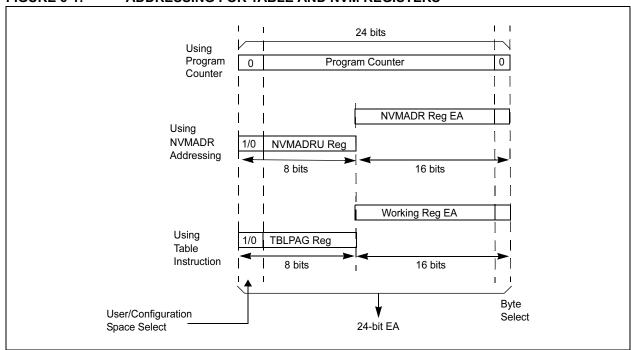

The program address space is 4M instruction words. It is addressable by the 23-bit PC, table instruction Effective Address (EA), or data space EA, when program space is mapped into data space, as defined by Table 3-1. Note that the program space address is incremented by two between successive program words, in order to provide compatibility with data space addressing.

User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE), for all accesses other than TBLRD/TBLWT, which use TBLPAG<7> to determine user or configuration space access. In Table 3-1, Read/Write instructions, bit 23 allows access to the Device ID, the User ID and the configuration bits. Otherwise, bit 23 is always clear.

FIGURE 3-1: PROGRAM SPACE MEMORY MAP FOR dsPIC30F6010

TABLE 3-1: PROGRAM SPACE ADDRESS CONSTRUCTION

| Access Type              | Access                        |      | Progra    | m Space A | ddress         |      |

|--------------------------|-------------------------------|------|-----------|-----------|----------------|------|

| Access Type              | Space                         | <23> | <22:16>   | <15>      | <14:1>         | <0>  |

| Instruction Access       | User                          | 0    |           | PC<22:1>  |                | 0    |

| TBLRD/TBLWT              | User<br>(TBLPAG<7> = 0)       | TBL  | PAG<7:0>  |           | Data EA <15:0> |      |

| TBLRD/TBLWT              | Configuration (TBLPAG<7> = 1) | TBL  | .PAG<7:0> |           | Data EA <15:0> |      |

| Program Space Visibility | User                          | 0    | PSVPAG<   | 7:0>      | Data EA <1     | 4:0> |

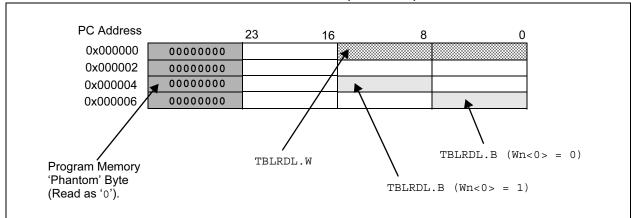

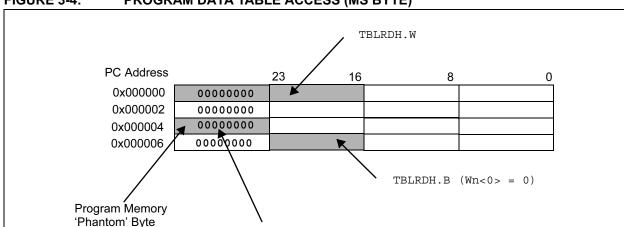

# 3.1.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

This architecture fetches 24-bit wide program memory. Consequently, instructions are always aligned. However, as the architecture is modified Harvard, data can also be present in program space.

There are two methods by which program space can be accessed; via special table instructions, or through the remapping of a 16K word program space page into the upper half of data space (see Section 3.1.2). The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the LS Word of any address within program space, without going through data space. The TBLRDH and TBLWTH instructions are the only method whereby the upper 8 bits of a program space word can be accessed as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the LS Data Word, and TBLRDH and TBLWTH access the space which contains the MS Data Byte.

Figure 3-2 shows how the EA is created for table operations and data space accesses (PSV = 1). Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

A set of Table Instructions are provided to move byte or word sized data to and from program space.

TBLRDL: Table Read Low Word: Read the LS Word of the program address;

P<15:0> maps to D<15:0>.

Byte: Read one of the LS Bytes of the program address:

P<7:0> maps to the destination byte when byte select = 0;

P<15:8> maps to the destination byte when byte select = 1.

- 2. **TBLWTL:** Table Write Low (refer to Section 6.0 for details on Flash Programming).

- TBLRDH: Table Read High Word: Read the MS Word of the program address;

P<23:16> maps to D<7:0>; D<15:8> always be = 0.

Byte: Read one of the MS Bytes of the program address;

P<23:16> maps to the destination byte when byte select = 0;

The destination byte will always be = 0 when byte select = 1.

TBLWTH: Table Write High (refer to Section 6.0 for details on Flash Programming).

FIGURE 3-3: PROGRAM DATA TABLE ACCESS (LS WORD)

TBLRDH.B (Wn < 0 > = 1)

#### FIGURE 3-4: PROGRAM DATA TABLE ACCESS (MS BYTE)

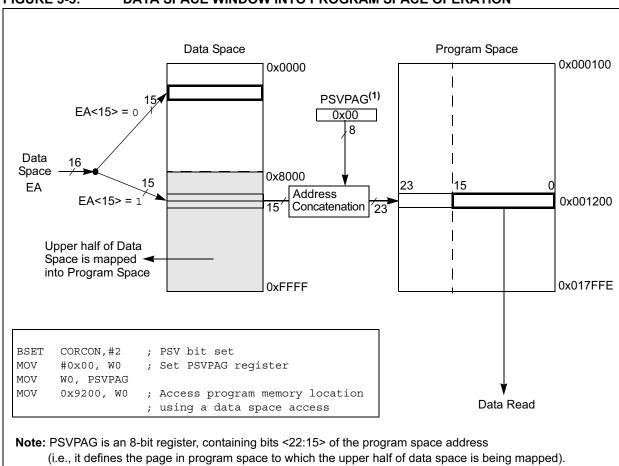

# 3.1.2 DATA ACCESS FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

(Read as '0')

The upper 32 Kbytes of data space may optionally be mapped into any 16K word program space page. This provides transparent access of stored constant data from X data space, without the need to use special instructions (i.e., TBLRDL/H, TBLWTL/H instructions).

Program space access through the data space occurs if the MS bit of the data space EA is set and program space visibility is enabled, by setting the PSV bit in the Core Control register (CORCON). The functions of CORCON are discussed in Section 2.4, DSP Engine.

Data accesses to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Note that the upper half of addressable data space is always part of the X data space. Therefore, when a DSP operation uses program space mapping to access this memory region, Y data space should typically contain state (variable) data for DSP operations, whereas X data space should typically contain coefficient (constant) data.

Although each data space address, 0x8000 and higher, maps directly into a corresponding program memory address (see Figure 3-5), only the lower 16-bits of the 24-bit program word are used to contain the data. The upper 8 bits should be programmed to force an illegal instruction to maintain machine robustness. Refer to the *dsPIC30F Programmer's Reference Manual* (DS70030) for details on instruction encoding.

Note that by incrementing the PC by 2 for each program memory word, the LS 15 bits of data space addresses directly map to the LS 15 bits in the corresponding program space addresses. The remaining bits are provided by the Program Space Visibility Page register, PSVPAG<7:0>, as shown in Figure 3-5.

**Note:** PSV access is temporarily disabled during Table Reads/Writes.

For instructions that use PSV which are executed outside a REPEAT loop:

- The following instructions will require one instruction cycle in addition to the specified execution time:

- MAC class of instructions with data operand pre-fetch

- MOV instructions

- MOV.D instructions

- All other instructions will require two instruction cycles in addition to the specified execution time of the instruction.

For instructions that use PSV which are executed inside a REPEAT loop:

- The following instances will require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

- Any other iteration of the REPEAT loop will allow the instruction, accessing data using PSV, to execute in a single cycle.

FIGURE 3-5: DATA SPACE WINDOW INTO PROGRAM SPACE OPERATION

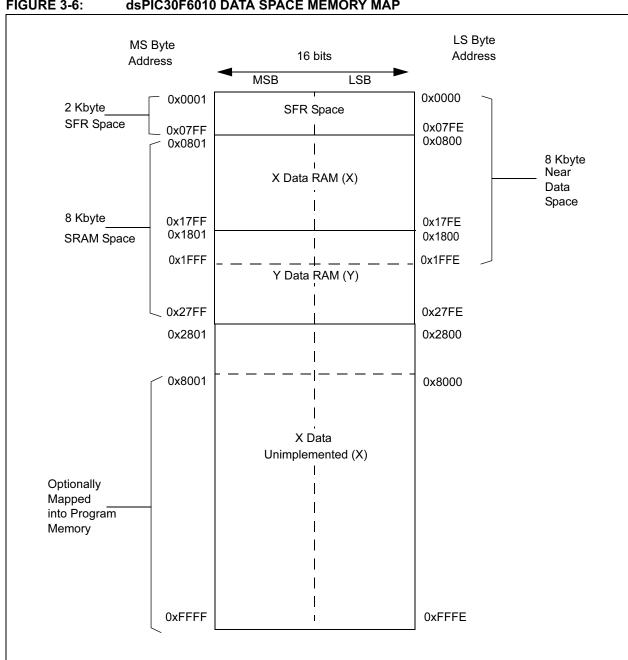

#### 3.2 Data Address Space

The core has two data spaces. The data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths.

#### 3.2.1 DATA SPACE MEMORY MAP

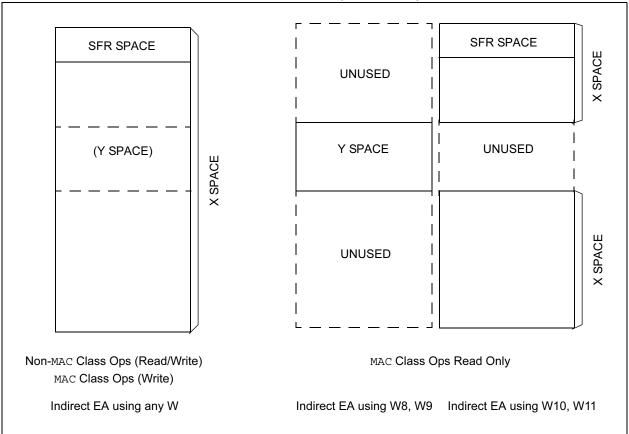

The data space memory is split into two blocks, X and Y data space. A key element of this architecture is that Y space is a subset of X space, and is fully contained within X space. In order to provide an apparent linear addressing space, X and Y spaces have contiguous addresses.

When executing any instruction other than one of the MAC class of instructions, the X block consists of the 64 Kbyte data address space (including all Y addresses). When executing one of the MAC class of instructions, the X block consists of the 64 Kbyte data address space excluding the Y address block (for data reads only). In other words, all other instructions regard the entire data memory as one composite address space. The MAC class instructions extract the Y address space from data space and address it using EAs sourced from W10 and W11. The remaining X data space is addressed using W8 and W9. Both address spaces are concurrently accessed only with the MAC class instructions.

A data space memory map is shown in Figure 3-6.

Figure 3-7 shows a graphical summary of how X and Y data spaces are accessed for MCU and DSP instructions.

© 2004 Microchip Technology Inc. Preliminary DS70119D-page 23

FIGURE 3-6: dsPIC30F6010 DATA SPACE MEMORY MAP

FIGURE 3-7: DATA SPACE FOR MCU AND DSP (MAC CLASS) INSTRUCTIONS EXAMPLE

#### 3.2.2 DATA SPACES

The X data space is used by all instructions and supports all addressing modes. There are separate read and write data buses. The X read data bus is the return data path for all instructions that view data space as combined X and Y address space. It is also the X address space data path for the dual operand read instructions (MAC class). The X write data bus is the only write path to data space for all instructions.

The X data space also supports Modulo Addressing for all instructions, subject to Addressing mode restrictions. Bit-Reversed Addressing is only supported for writes to X data space.

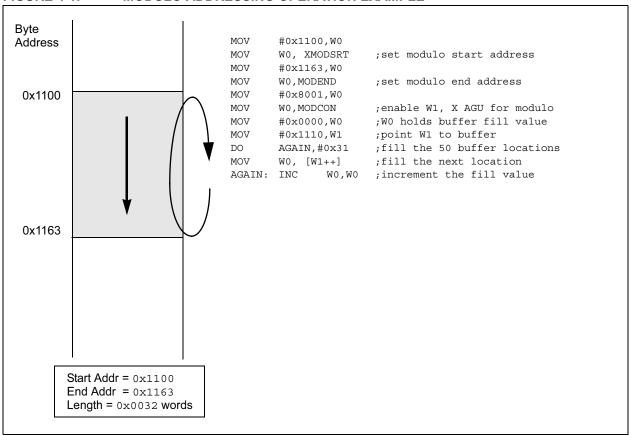

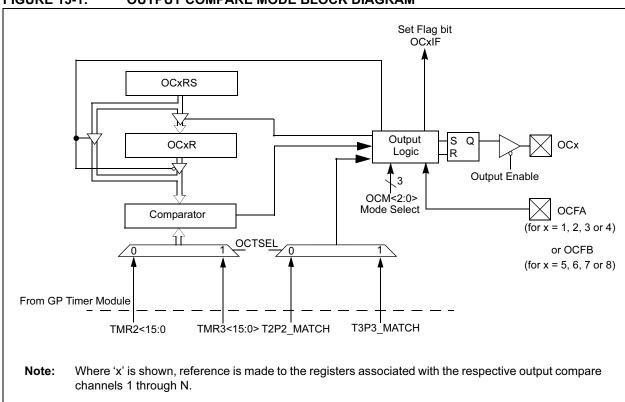

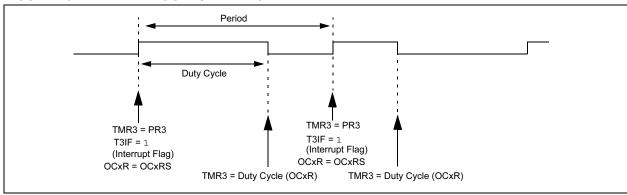

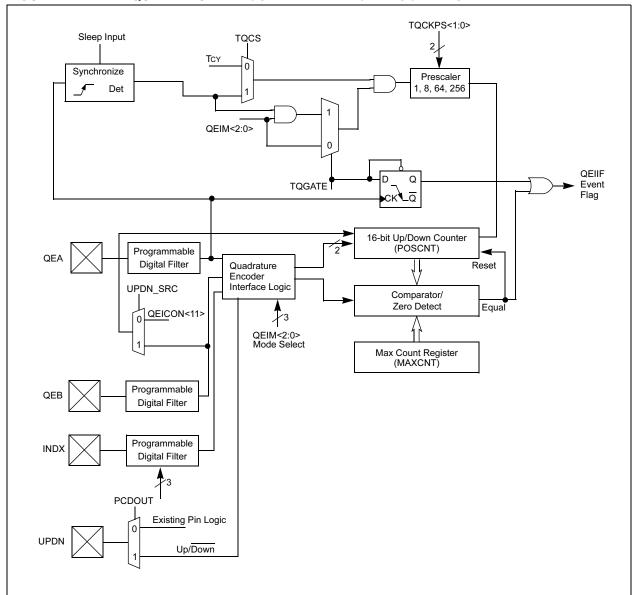

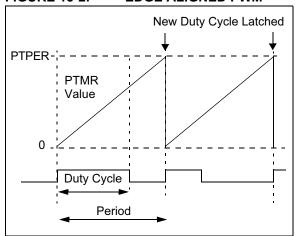

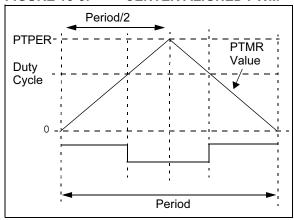

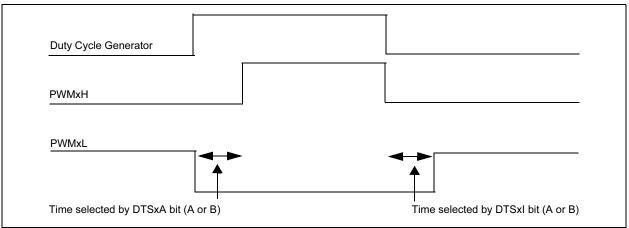

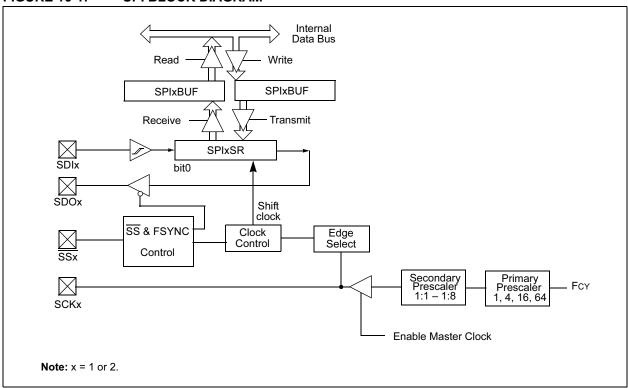

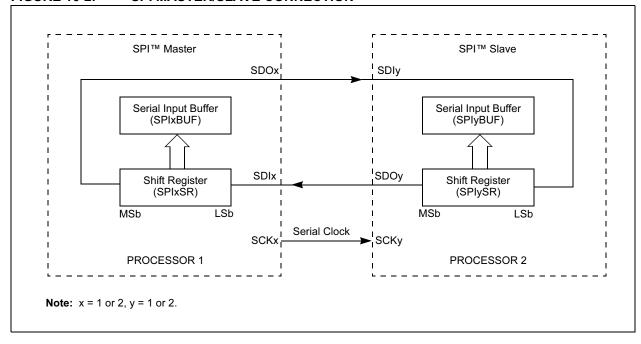

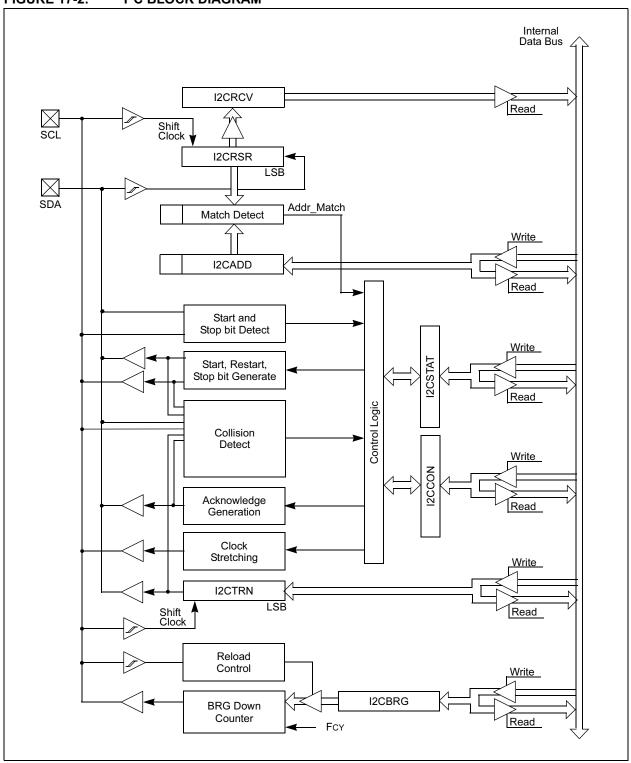

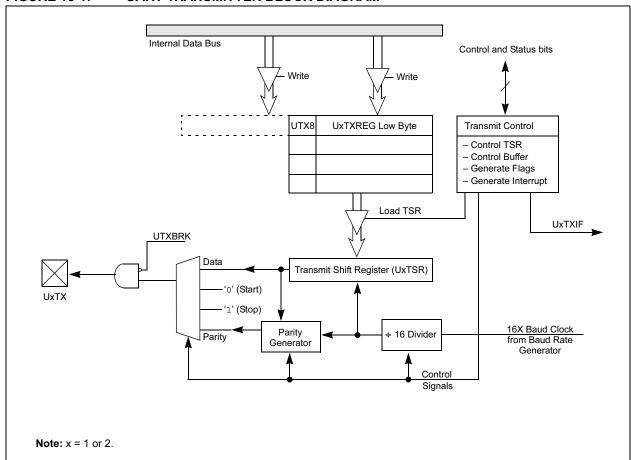

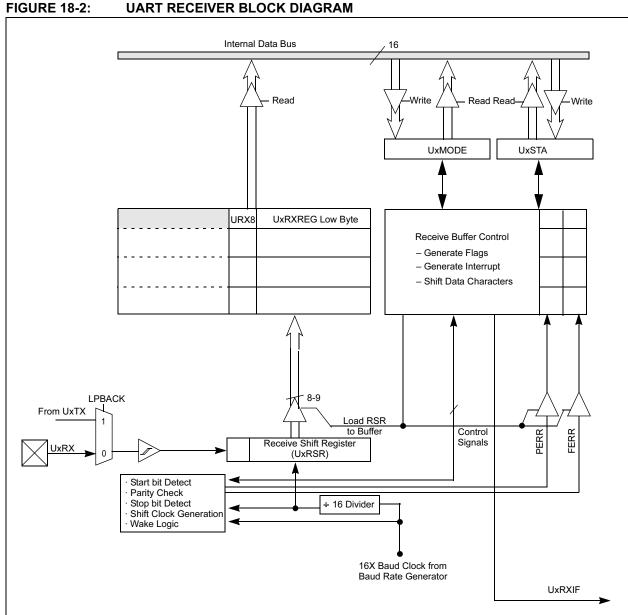

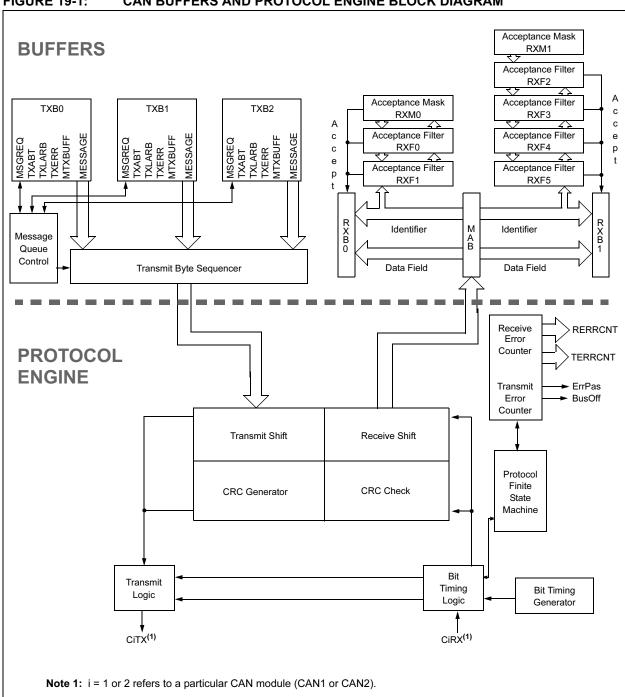

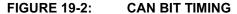

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths. No writes occur across the Y bus. This class of instructions dedicates two W register pointers, W10 and W11, to always address Y data space, independent of X data space, whereas W8 and W9 always address X data space. Note that during accumulator write back, the data address space is considered a combination of X and Y data spaces, so the write occurs across the X bus. Consequently, the write can be to any address in the entire data space.